## **Utah State University**

# DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

5-2015

# Design of Reliable and Secure Network-On-Chip Architectures

Dean Michael B Ancajas Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Ancajas, Dean Michael B, "Design of Reliable and Secure Network-On-Chip Architectures" (2015). All Graduate Theses and Dissertations. 4150.

https://digitalcommons.usu.edu/etd/4150

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

# DESIGN OF RELIABLE AND SECURE NETWORK-ON-CHIP ${\bf ARCHITECTURES}$

by

Dean Michael B Ancajas

A dissertation submitted in partial fulfillment of the requirements for the degree

of

DOCTOR OF PHILOSOPHY

in

Electrical Engineering

| Approved:               |                                        |

|-------------------------|----------------------------------------|

|                         |                                        |

| Dr. Koushik Chakraborty | Dr. Sanghamitra Roy                    |

| Major Professor         | Committee Member                       |

| Dr. Todd Moon           | Dr. Chris Winstead                     |

| Committee Member        | Committee Member                       |

| Dr. Dan Watson          | Dr. Mark R. McLellan                   |

| Committee Member        | Vice President for Research and        |

|                         | Dean of the School of Graduate Studies |

$\begin{array}{c} \text{UTAH STATE UNIVERSITY} \\ \text{Logan, Utah} \end{array}$

Copyright © Dean Michael B Ancajas 2015

All Rights Reserved

Abstract

Design of Reliable and Secure Network-on-Chip Architectures

by

Dean Michael B Ancajas, Doctor of Philosophy

Utah State University, 2015

Major Professor: Dr. Koushik Chakraborty

Department: Electrical and Computer Engineering

Network-on-Chips (NoCs) have become the standard communication platform for future massively parallel systems due to their performance, flexibility and scalability advan-

tages. However, reliability issues brought about by scaling in the sub-20nm era threaten to

undermine the benefits offered by NoCs. This dissertation demonstrates design techniques

that address both reliability and security issues facing modern NoC architectures. The

reliability and security problem is tackled at different abstraction levels using a series of

schemes that combine information from the architecture-level as well as hardware-level in

order to combat aging effects and meet secure design stipulations while maintaining modest

power-performance overheads.

(128 pages)

iv

Public Abstract

Design of Reliable and Secure Network-on-Chip Architectures

by

Dean Michael B Ancajas, Doctor of Philosophy

Utah State University, 2015

Major Professor: Dr. Koushik Chakraborty

Department: Electrical and Computer Engineering

The trend towards massive parallel computing has necessitated the need for an On-Chip communication framework that can scale well with the increasing number of cores. At the same time, technology scaling has made transistors susceptible to a multitude of reliability issues. This dissertation demonstrates design techniques that address both reliability and security issues facing modern NoC architectures. The reliability and security problem is tackled at different abstraction levels using a series of schemes that combine information from the architecture-level as well as hardware-level in order to combat aging effects and

meet secure design stipulations while maintaining modest power-performance overheads.

This dissertation is lovingly dedicated to my parents, Norma Ancajas and Danilo Ancajas, and to my brothers and sister: Diana, Jan and Norman. Their support, encouragement and constant love have sustained me throughout my life.

# Acknowledgments

I would like to express my gratitude to the many persons who have helped me during my PhD years. To my committee chair, Dr. Koushik Chakraborty, and my co-advisor, Dr. Sanghamitra Roy, for their advice, patience, financial support and guidance throughout my entire tenure as a PhD student. They have given me the opportunity to work on various high-impact research topics and have influenced the way I think about various issues both in my professional and personal life. To all of my committee members, Dr. Todd Moon, Dr. Chris Winstead and Dr. Dan Watson, for their valuable insights and comments on this research. I also want to thank them for supporting me, despite numerous obstacles and tough situations, in obtaining a summer internship during my final year at USU.

I would also like to thank members of the Bridge Lab—those who have moved on already, those currently enjoying doing research, and those just beginning—for their companionship, support and friendship. Thank you to Kshitij for being an excellent roommate and friend; Yiding for the friendship and those late-night coding sprees to finish our global routing program; Jason for the work we did in the Exascale NoC and Fort-NoCs; Saurabh for the opportunity to work on the NBTI-aware register file design; Satyajit and Gopal for the friendship and the fun racquet ball games; Hu Chen for the fun conversations about life and research; and Rajesh for continuing the work on NoC reliability/security. I would like to acknowledge several students who have helped me one way or another: McCabe, Brennan, Manzi, Brian, Prabal, Shayan, Chidham, Shamik, Harshita, Jacob, Andrew, Niranjan, Ashish, Soojeong and Jamy.

My deepest appreciation goes to the ECE Department and all of the staff members, for giving me the opportunity to pursue my PhD studies. I am very thankful to Mary Lee Anderson and Tricia Brandenburg for the invaluable support in helping me solve various administrative matters; Trent Johnson and Scott Kimber for the prompt technical support and the condor pool maintenance; you have contributed greatly in allowing me to beat paper deadlines.

vii

Last, but certainly not least, I would like to thank my significant other, Tanya Abaya, for being my partner in crime and for experiencing life together; my good friend Julio Martin, for the fun times and adventures we undertook in Logan; my families: the Ancajas-es, Blascos, Calabias and the Rabes for the neverending support throughout my career.

Dean Michael B Ancajas

# Contents

|    |       |                                                                           | Page        |

|----|-------|---------------------------------------------------------------------------|-------------|

| Al | ostra | ${f ct}$                                                                  | . iii       |

| Pι | ıblic | Abstract                                                                  | . <b>iv</b> |

| A  | cknov | wledgments                                                                | vi          |

| Li | st of | Tables                                                                    | . xi        |

| Li | st of | Figures                                                                   | xii         |

|    |       | /ms                                                                       |             |

| A  | rony  | 'ms                                                                       | . <b>XV</b> |

| 1  | Intr  | $\operatorname{roduction}$                                                | 1           |

|    | 1.1   | Contributions of This Research                                            | 2           |

|    |       | 1.1.1 Conference Papers                                                   | 3           |

|    |       | 1.1.2 Journal Paper                                                       | 3           |

|    | 1.2   | Tackling QoS-induced Aging in Exascale Systems                            | 3           |

|    | 1.3   | HCI Tolerant NoC Router Microarchitecture                                 | 5           |

|    | 1.4   | Proactive Aging Management in Heterogeneous Network-on-Chips              | 6           |

|    | 1.5   | Fort-NoCs: Mitigating the Threat of a Compromised-NoC                     | 8           |

| 2  | Lite  | erature Survey and Related Work                                           | . 10        |

|    | 2.1   | State-of-the-Art in NoC Research                                          | 10          |

|    | 2.2   | Reliability Considerations for Exascale Systems                           | 19          |

|    | 2.3   | Reliability Design in $hNoCs$                                             | 19          |

|    | 2.4   | HCI-Aware Design of NoCs                                                  | 20          |

|    | 2.5   | Landscape of Security for NoCs                                            | 21          |

| 3  | Reli  | iability for Heterogeneous NoCs                                           | . 23        |

|    | 3.1   | Motivation                                                                | 23          |

|    |       | 3.1.1 Utilization Asymmetry in Heterogeneous NoCs                         | 24          |

|    |       | 3.1.2 Criticality of Different Flits in NoCs                              | 24          |

|    |       | 3.1.3 Significance for Reliability Driven Routing in Heterogeneous NoCs . | 26          |

|    | 3.2   | Design: Aging-Driven Routing via Packet-Criticality                       | 26          |

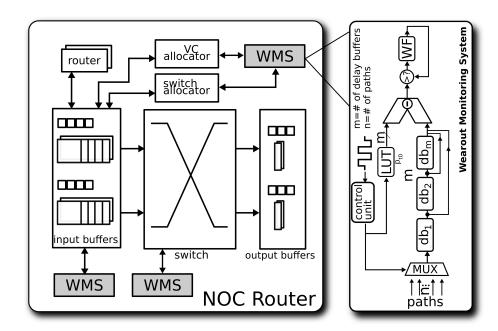

|    |       | 3.2.1 Wearout Monitoring System for NoC Routers                           | 27          |

|    |       | 3.2.2 Criticality-Driven Path Selection                                   | 28          |

|    | 3.3   | Aging Model for an hNoC                                                   | 30          |

|    | -     | 3.3.1 NBTI Impact on Routers and Links                                    | 30          |

|    |       | 3.3.2 NBTI Effect on Heterogeneous NoC                                    | 31          |

|    | 3.4   | Methodology                                                               | 33          |

|    |       | 3.4.1 NoC Reliability Evaluation                                          | 33          |

| 1   | v         |

|-----|-----------|

| - 1 | $\Lambda$ |

|   |     | 3.4.2 Lifetime Simulation                                               |

|---|-----|-------------------------------------------------------------------------|

|   | 3.5 | Results                                                                 |

|   |     | 36 Routing Schemes                                                      |

|   |     | 37 B.5.2 Performance Analysis                                           |

| 4 | HC  | Tolerant NoC Router Microarchitecture                                   |

|   | 4.1 | Background                                                              |

|   | 4.2 | Motivation                                                              |

|   |     | 4.2.1 HCI Degradation in the NoC Crossbar                               |

|   |     | 4.2.2 Aging Analysis Framework for the NoC Crossbar                     |

|   |     | 42.3 Results                                                            |

|   | 4.3 | Design Overview                                                         |

|   |     | 44.3.1 Bit Cruising (BC)                                                |

|   |     | 1.3.2 Distribution Cycle Mode (DCM)                                     |

|   |     | 1.3.3 Crossbar Lane Switching (CLS)                                     |

|   |     | 1.3.4 Bit Cruising and Crossbar Lane Switching (BCCLS)                  |

|   | 4.4 | Methodology                                                             |

|   |     | 4.4.1 Architectural Setup                                               |

|   |     | 1.4.2 RTL and Switching Activity Simulation                             |

|   |     | 4.4.3 HCI Degradation Analysis                                          |

|   | 4.5 | Results                                                                 |

|   |     | 4.5.1 Comparative Schemes and Evaluation Metrics                        |

|   |     | 4.5.2 Switching Activity Distribution                                   |

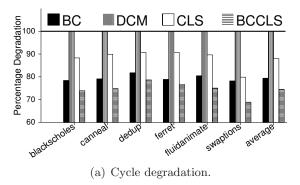

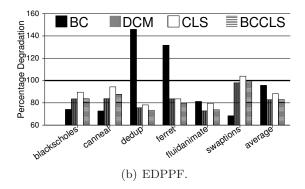

|   |     | 1.5.3 Clock Cycle Degradation                                           |

|   |     | 4.5.4 Energy Delay Product Per Flit (EDPPF) 60                          |

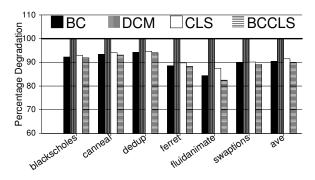

|   |     | 1.5.5 System Performance                                                |

| 5 | Tac | ing QoS-induced Aging in Exascale NoCs 63                               |

| • | 5.1 | Motivation                                                              |

|   |     | 5.1.1 Scalability Impact on NoC Wearout                                 |

|   |     | 5.1.2 QoS Support and NoC Lifetime                                      |

|   |     | 5.1.3 Significance                                                      |

|   | 5.2 | Design of Wearout Resilient Routing in an Exascale NoC                  |

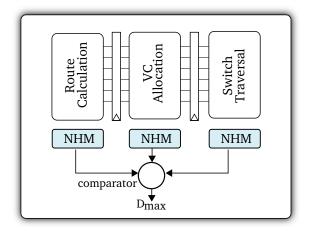

|   |     | 5.2.1 NoC Health Meter (NHM)                                            |

|   |     | 5.2.2 Propagating Delay Information and Routing Table Update 69         |

|   |     | 5.2.3 Routing Algorithm                                                 |

|   |     | 5.2.4 Applying NoC Health Meter in Dynamic Wearout Resilient Routing 72 |

|   | 5.3 | Methodology                                                             |

|   |     | 5.3.1 Hierarchical Reliability Evaluation                               |

|   |     | 5.3.2 Lifetime Simulation                                               |

|   | 5.4 | Experimental Results                                                    |

|   |     | 5.4.1 MTTF: Fault Model and Comparison                                  |

|   |     | 5.4.2 Quality-of-Service                                                |

|   |     | 5.4.3 Performance                                                       |

| 6            | Fort  | t-NoCs | s: Mitigating the Threat of a Compromised-NoC (C-NoC) 83 |

|--------------|-------|--------|----------------------------------------------------------|

|              | 6.1   | Threa  | t of a C-NoC                                             |

|              |       | 6.1.1  | Threat Overview                                          |

|              |       | 6.1.2  | Threat Relevance                                         |

|              | 6.2   | Evalua | ating a C-NoC                                            |

|              |       | 6.2.1  | Design Overview                                          |

|              |       | 6.2.2  | Design Footprint                                         |

|              |       | 6.2.3  | Runtime Overhead                                         |

|              | 6.3   | Mitiga | ating the Threat of a C-NoC                              |

|              |       | 6.3.1  | Layer 1: Data Scrambling (DS)                            |

|              |       | 6.3.2  | Layer 2: Packet Certification (PC)                       |

|              |       | 6.3.3  | Layer 3: Node Obfuscation                                |

|              | 6.4   | Potent | tial Spoofing Attacks                                    |

|              | 6.5   |        | imental Results                                          |

|              |       | 6.5.1  | Implementation                                           |

|              |       | 6.5.2  | Area and Power                                           |

|              |       | 6.5.3  | Performance                                              |

| 7            | Con   | clusio | n                                                        |

| $\mathbf{R}$ | efere | nces   |                                                          |

| <b>1</b> 7   | ita   |        | 111                                                      |

# List of Tables

| Table |                                                                                                     | Page |

|-------|-----------------------------------------------------------------------------------------------------|------|

| 2.1   | Comparison of threats in NoCs                                                                       | 22   |

| 3.1   | Packet-criticality classification                                                                   | 26   |

| 3.2   | WF-based deflection estimation                                                                      | 30   |

| 3.3   | Delay distribution for buffered (high utilization) and bufferless (low utilization) routers in BRAR |      |

| 4.1   | Logic depth of various modules                                                                      | 43   |

| 4.2   | Pertinent transitions of various gates                                                              | 56   |

| 6.1   | Design footprint of the NoC trojan hardware                                                         | 87   |

| 6.2   | States of the trojan                                                                                | 89   |

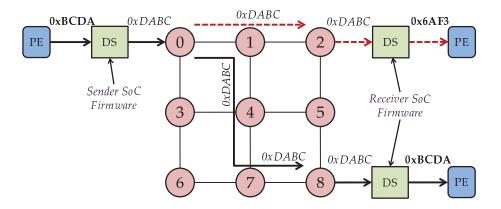

| 6.3   | Possible decoding of 0xDABC at different nodes                                                      | 92   |

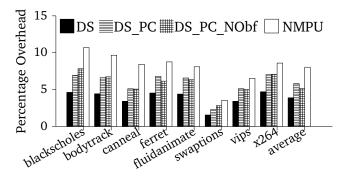

| 6.4   | Overhead of security schemes                                                                        | 99   |

# List of Figures

| Figure |                                                                                                                                                                                                        | Page |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

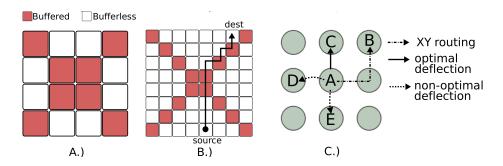

| 3.1    | A.) $4\times4$ mesh configuration B.) BRAR routing on an $8\times8$ mesh C.) Deflection routing on bufferless routers                                                                                  | 25   |

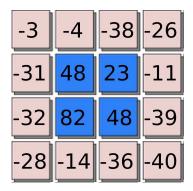

| 3.2    | Percentage traffic increase of each router using BRAR (average across PAR-SEC benchmarks). This utilization difference leads to more than $2\times$ divergence in NBTI-induced performance degradation | 27   |

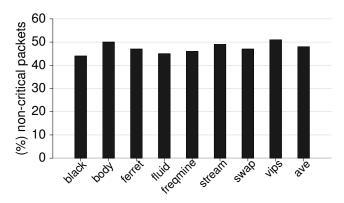

| 3.3    | Percentage of non-critical data packets routed through the buffered routers.                                                                                                                           | 27   |

| 3.4    | WMS circuit. Each path delay is sampled through a buffer sequence and compared with the reference delay to calculate the WF                                                                            | 29   |

| 3.5    | Reliability-aware framework                                                                                                                                                                            | 34   |

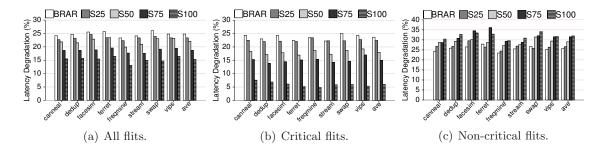

| 3.6    | Latency degradation of different types of flits in $hNoC$ (lower is better)                                                                                                                            | 39   |

| 3.7    | Performance and EDPPF degradation (lower is better)                                                                                                                                                    | 39   |

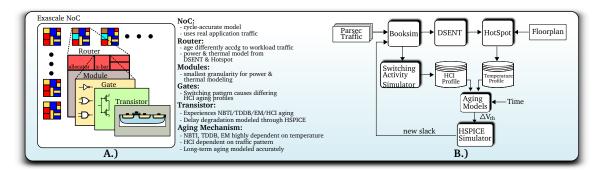

| 4.1    | HCI aging analysis framework                                                                                                                                                                           | 45   |

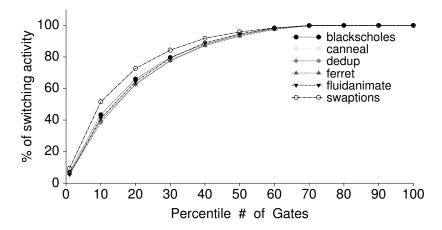

| 4.2    | Cumulative distribution function of the switching activity vs gate count                                                                                                                               | 46   |

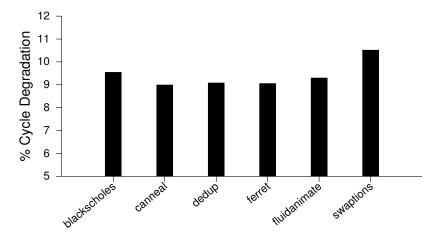

| 4.3    | Clock cycle degradation of a 22nm NoC router due to HCI after 7 years                                                                                                                                  | 46   |

| 4.4    | Bit cruiser circuit.                                                                                                                                                                                   | 47   |

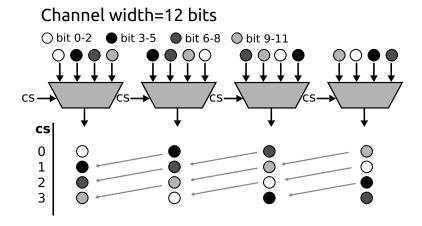

| 4.5    | Time lapse example of a bit cruiser circuit for a 12-bit channel. Signal cs is the cruise setting                                                                                                      | 47   |

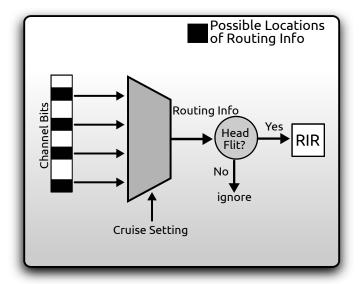

| 4.6    | Routing information extraction circuit                                                                                                                                                                 | 49   |

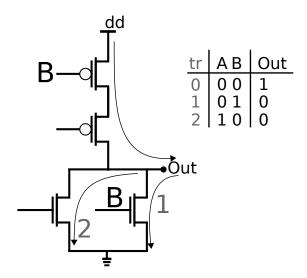

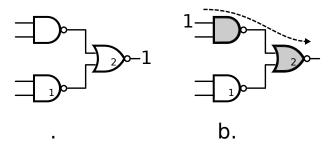

| 4.7    | Two-bit NOR gate showing the different transitions with respect to inputs.                                                                                                                             | 50   |

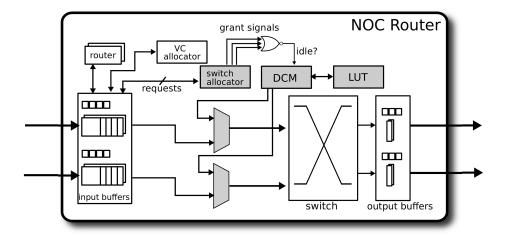

| 4.8    | Modified NoC router to accommodate DCM operation                                                                                                                                                       | 51   |

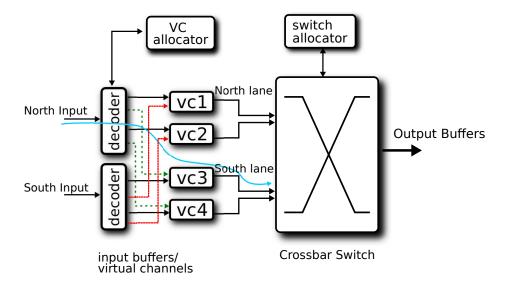

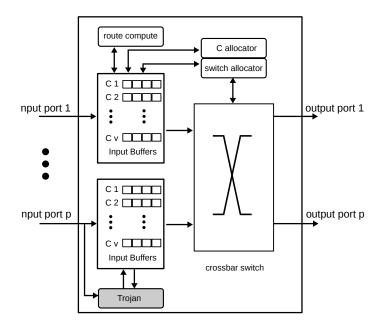

| 4.9    | Baseline implementation of an NoC router showing the virtual channels, input ports and the crossbar switch. Output ports and output virtual channels are not shown                                     | 53   |

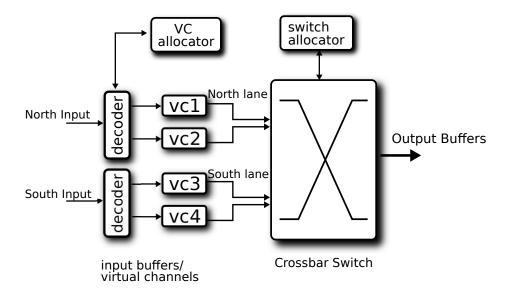

| 4.10   | CLS implementation. VC allocator can assign incoming flits to any virtual channel                                                                                                                      | 54   |

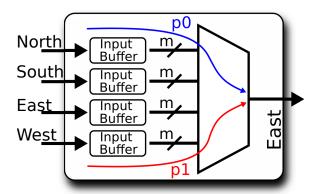

| 4.11 | East section of a crossbar switch. CLS works on the <b>inter</b> -lane <sup>3</sup> (by changing the path of the data) level while BC works only on the <b>intra</b> -lane level (by changing the bit ordering within a path) | 55 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.12 | HCI analysis                                                                                                                                                                                                                  | 58 |

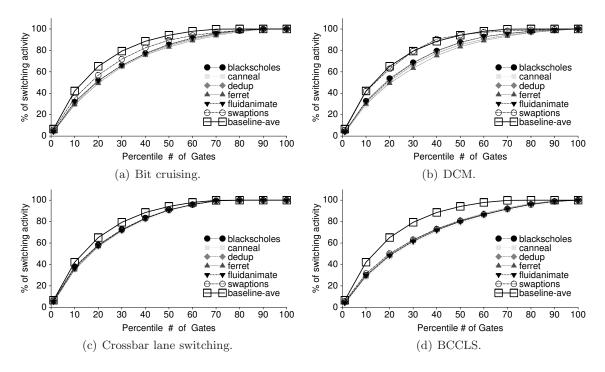

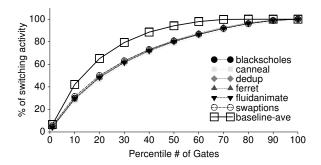

| 4.13 | Cumulative Distribution Graph of BC, DCM and CLS schemes. Solid line in each graph is the baseline average (lower is better)                                                                                                  | 60 |

| 4.14 | CDF for BCCLS scheme.                                                                                                                                                                                                         | 60 |

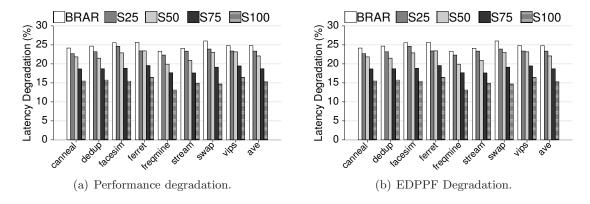

| 4.15 | Router Cycle time Degradation and Energy Delay Product Per Flit. Solid line indicates baseline (lower is better)                                                                                                              | 61 |

| 4.16 | System performance degradation (lower is better)                                                                                                                                                                              | 62 |

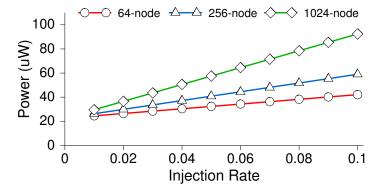

| 5.1  | Effect of scaling on average router power consumption (16nm node)                                                                                                                                                             | 64 |

| 5.2  | Trend for scaling impact on MTTF (16nm node)                                                                                                                                                                                  | 65 |

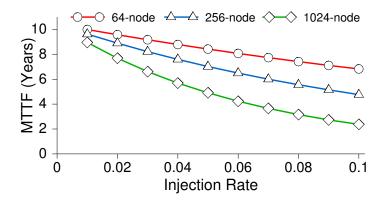

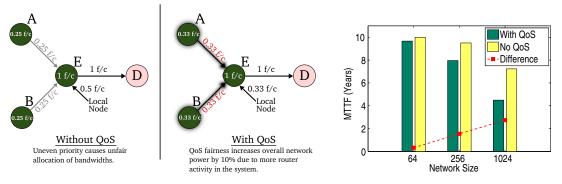

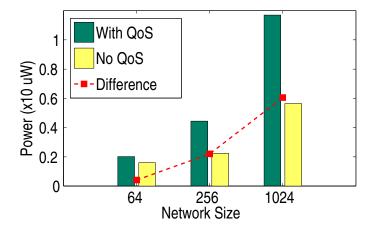

| 5.3  | Conflicting goals of QoS support and sustainability: although the bandwidth offered by the NoC remains unchanged, different resource usage under QoS causes an accelerated wearout and a shortened lifetime                   | 67 |

| 5.4  | Effect of providing QoS on the average router power consumption                                                                                                                                                               | 67 |

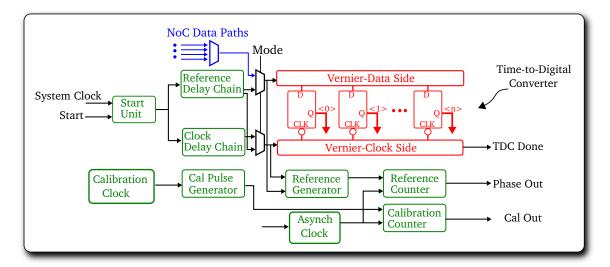

| 5.5  | High resolution in situ delay slack measurement from Fick et al. [75]                                                                                                                                                         | 70 |

| 5.6  | NoC router augmented with NHM                                                                                                                                                                                                 | 71 |

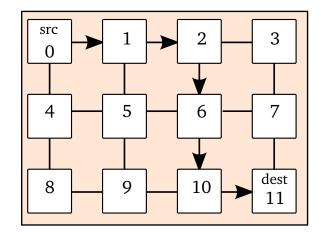

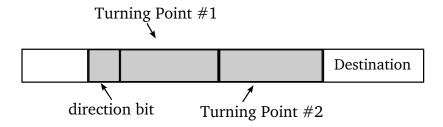

| 5.7  | Two-turn path routing                                                                                                                                                                                                         | 73 |

| 5.8  | Head flit: unused fields can be used to store additional algorithmic routing information                                                                                                                                      | 73 |

| 5.9  | Reliability-aware framework                                                                                                                                                                                                   | 77 |

| 5.10 | NoC performance of blackscholes under progressive aging in various schemes.                                                                                                                                                   | 79 |

| 5.11 | MTTF (higher is better)                                                                                                                                                                                                       | 80 |

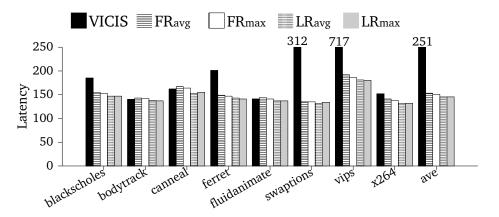

| 5.12 | QoS:jitter (lower is better)                                                                                                                                                                                                  | 81 |

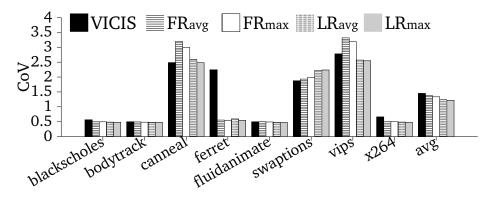

| 5.13 | QoS:CoV (lower is better)                                                                                                                                                                                                     | 81 |

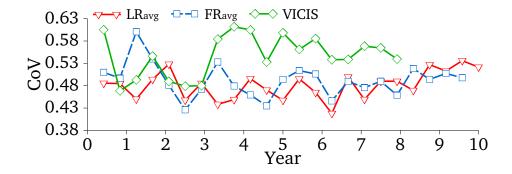

| 5.14 | QoS:Blackscholes CoV (lower is better)                                                                                                                                                                                        | 82 |

| 5 15 | Latency (lower is better)                                                                                                                                                                                                     | 82 |

|     |                                                                                                        | xiv |

|-----|--------------------------------------------------------------------------------------------------------|-----|

| 6.1 | Compromised NoC snooping data messages between programs A & B, and leaking to the accomplice program C | 85  |

| 6.2 | Compromised NoC with hardware trojan                                                                   | 88  |

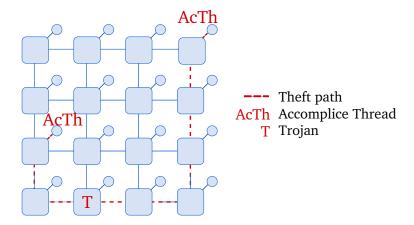

| 6.3 | Trojan with two possible locations of AcTh. The length of the theft path depends on where the AcTh is  | 89  |

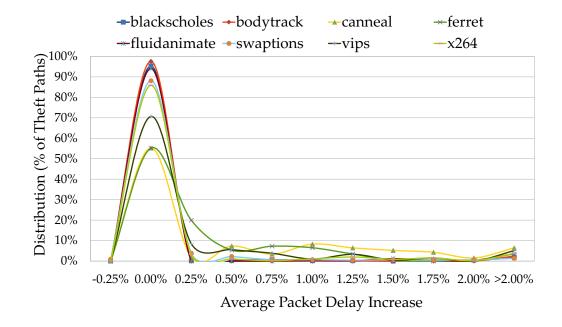

| 6.4 | Runtime performance overhead. The figure shows overhead distribution across all possible theft paths   | 90  |

| 6.5 | Fort-NoCs design perspective                                                                           | 91  |

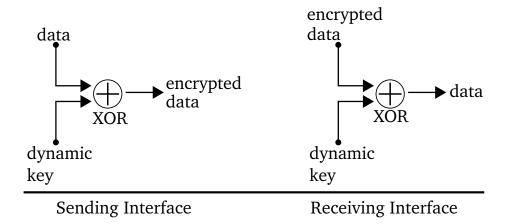

| 6.6 | Low-overhead XOR cipher allows encryption/decryption using dynamic keys from the firmware              | 93  |

| 6.7 | Example for DS                                                                                         | 93  |

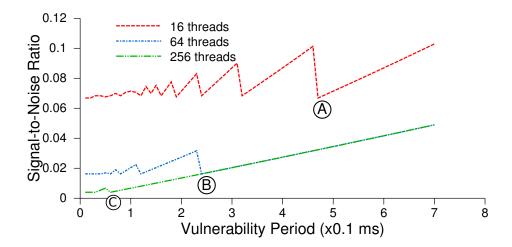

| 6.8 | Side-channel resilience comparison (lower is better)                                                   | 98  |

# Acronyms

AcTh Accomplice Thread

ALU Arithmetic Logic Unit

BC Bit Cruising

BCCLS Bit Cruising & Crossbar Lane Switching

BRAR Buffered-Router Aware Routing

CAM Content-Addressable Memory

CDF Cumulative Distribution Function

CMP Chip Multiprocessor

CMOS Complimentary Metal Oxide Semiconductor

CLS Crossbar Lane Switching

CS Cruise Setting

C-NoC Compromised NoC

DSENT Design Space Exploration for Network Tool

DC Direct Current

DS Data Scrambling

DCM Distributed Cycle Mode

EDPPF Energy Delay-Product per Flit

HAAF HCI Aging Analysis Framework

hNoC Heterogeneous Network-on-Chip

IB Input Buffers

IP Intellectual Property

NoC Network-on-Chip

EM Electromigration

HCI Hot-Carrier Injection

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MPSoC Multiprocessor SoC

NI Network Interface

NBTI Negative Bias Temperature Instability

NMOS n-channel MOSFET

NObf Node Obfuscation

OCP Open Core Protocol

OS Operating System

PMOS p-channel MOSFET

PDF Probability Distribution Function

PC Packet Certification

PE Processing Element

PLB Permission Lookaside Table

RC Route Calculation

RTL Register Transfer Level

RIE Routing Information Extraction

RIR Routing Information Register

SA Switch Allocators

SoC System-on-Chip

SNR Signal-to-Noise Ratio

SVP Single Vulnerability Period

SRAM Static Random Access Memory

TDDB Time-Dependent Dielectric Breakdown

TSMC Taiwan Semiconductor Manufacturing Company

VC Virtual Channel

VPI Verilog Procedural Interface

WF Wearout Factor

WMS Wearout Monitoring System

# Chapter 1

## Introduction

Rapid technology scaling has fueled an unprecedented growth in the semiconductor industry, transforming the face of modern society. Commodity systems have undergone a sea change from the uniprocessor era of past decades to the current multicore era. Furthermore, the prospect of many-core systems in the near future looms large. With numerous on-chip processing cores, the communication fabric in many-core systems becomes a critical design component. Network-on-Chip (NoC) architectures are widely touted as the most promising design for the communication platform for future many-core systems, primarily due to their scalability. Many-core prototypes such as the Intel 80-core, Intel Single Chip Cloud system and Tilera have already used NoCs as the backbone of communication between their on-chip processors [1, 2].

Continuous technology scaling also causes a rapid deterioration in the device-level robustness, forcing the need for fault-resilient system design. While a large body of recent works targets on-chip computing resources (processing cores), the emergence of the many-core era has raised the importance of addressing the sustainability of on-chip communication architectures such as NoCs. Future many-core systems, comprising abundant rudimentary in-order cores can lack in their individual ability to hide network latency [2]. Consequently, aging-induced performance degradation in the NoC can create a serious bottleneck, undermining system-level efficiency and reliability. With economic viability playing a central role in both personal and corporate decision making, it is imperative to ensure sustained lifetime in both NoCs and processing cores, in order to have a meaningful impact at the system level.

In this context, this dissertation addresses sustainability challenges in NoC architectures while preserving system-level efficiency. Merely optimizing for power-performance efficiency creates a fundamental tension in the NoC design spectrum. Existing state-of-theart techniques for NoCs attempt to tackle this tension in a reactive manner by focusing solely on power-performance until a component failure occurs, after which corrective measures are triggered [3–7]. This work presents a series of proactive orthogonal approaches, simultaneously addressing the need for aging-awareness while preserving system power-performance efficiency in NoCs.

Thwarting aging-induced latency degradation in NoCs can be instrumental in designing sustainable future many-core systems. The techniques proposed in this work can expand the time span of fault-free execution in the NoC through symmetric and graceful aging degradation. This dissertation also demonstrates that under certain situations, aging resilience can be provided in NoCs without sacrificing power-performance. This intriguing property, achieved by recognizing the criticality aspects of on-chip communication, can spawn similar effective techniques in the pursuit of balancing power-performance and robustness in NoC architectures.

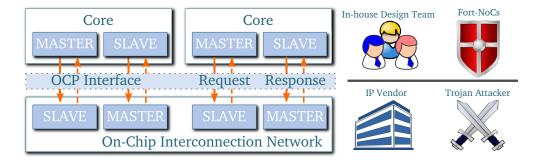

This dissertation also addresses a new emerging challenge in the design of NoCs: Security. As System-on-Chip development grows in complexity and cost, there is an increasing emphasis on employing third party IP NoC blocks to connect components for cost-reduction purposes. One of the key assumptions in trustworthy computing is that the software is running on top of a fully secure hardware. With tight time-to-market deadlines and increasing popularity of 3rd party Intellectual Property (3PIP) use, this assumption does not hold true anymore and causes current security techniques to be circumvented. In particular, a series of low overhead approaches where the system security is maintained in the presence of an information-leaking HW trojan embedded by a malicious 3PIP designer.

### 1.1 Contributions of This Research

The findings from this research are very promising, with one work being nominated for a Best Paper Award in 2014 IEEE International Conference in Hardware/Software Codesign and System Synthesis (CODES+ISSS). Several publications stemming from this dissertation can also be found in the proceedings of the 2013 & 2014 IEEE/ACM Design

Automation Conferences (DAC), 2013 IEEE/ACM Design, Automation and Test in Europe (DATE) and 2014 IEEE Transactions on Very Large Scale Integration (TVLSI).

Publications made during this period of research are listed as follows:

#### 1.1.1 Conference Papers

- Tackling QoS-induced Aging in Exascale Systems. Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy. 2014 IEEE International Conference in Hardware/Software Codesign and System Synthesis (CODES+ISSS)

- Fort-NoCs: Mitigating the Threat of a Compromised-NoC. Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy. 2014 IEEE/ACM Design Automation Conference.

- HCI-Tolerant Network-On-Chip Router Microarchitecture. Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy. 2013 IEEE/ACM Design Automation Conference.

- Proactive Aging Management in Heterogeneous Network-On-Chip Architectures. Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy. 2013 IEEE/ACM Design, Automation and Test in Europe (DATE)

#### 1.1.2 Journal Paper

Wearout Resilient Network-On-Chip Architecture. Dean Michael Ancajas, Koushik Chakraborty, Sanghamitra Roy. 2014 IEEE Transactions on Very Large Scale Integration (TVLSI).

## 1.2 Tackling QoS-induced Aging in Exascale Systems

This work shows that supporting QoS in an exascale NoC has profound implications on its reliability. Through experiments, it is shown that as a NoC is scaled, providing QoS

dramatically reduces its Mean Time To Failure (MTTF) due to the increased power consumption and elevated thermal profile. This increased power/thermal characteristics from QoS support does not come from a performance increase, rather from a more proportionate resource management enabled through QoS support [8]. Thus, although the NoC system continues to offer an identical bandwidth, QoS support results in an accelerated wearout and a reduced lifetime.

To effectively increase the lifetime of QoS-enabled exascale NoCs, this research introduces Dynamic Wearout Resilient Routing (DWRR) algorithms. The DWRR algorithms balance QoS and reliability impact by extenuating the additional stress induced by enforcing QoS guarantees in the system. The proposed schemes are based on a cross-layer theme, where device-level wearout is sensed at the circuit layer, and communicated to the architecture layer to dictate the routing path selection. Overall, the lifetime is increased by aiming to retain uniform wearout among all routers in an exascale NoC. To the best of the author's knowledge, this is the first work to tackle the tension between reliability and QoS in an exascale NoC.

The contributions of this work are as follows:

- Reliability Analysis of QoS and Scaling Effects in Exascale NoCs: An analysis of the reliability impact of providing QoS in large scale NoCs. The experiments in Section 5.1 show that the MTTF of a 1024-node NoC can be reduced by 36.6% (two years) of its rated lifetime just by supporting QoS. In the same light, as the number of nodes in the system are increased from 64 to 1024-nodes, the MTTF can be reduced by as much as 48%. These looming problems signify a need for managing the resources in an exascale NoC appropriately.

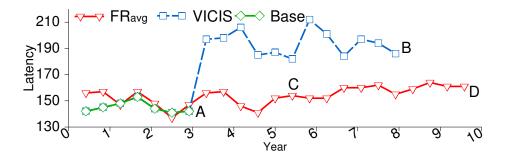

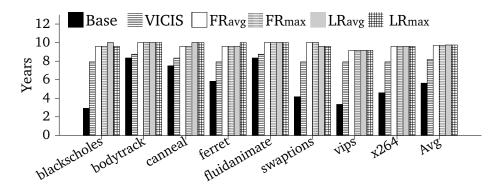

- **DWRR Algorithms:** This work also developed two novel DWRR algorithms (Section 5.2.4). The first algorithm, fresh routing (FR), lengthens NoC lifetime by always prioritizing the least degraded path at the cost of reduced QoS. The second algorithm, latency-reclamation routing (LR), gives balanced priority to aging and QoS.

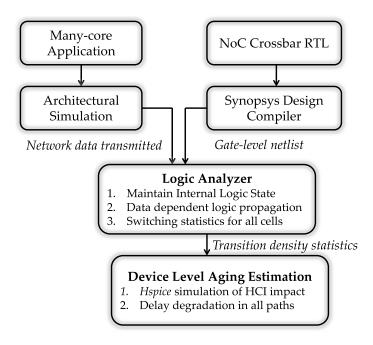

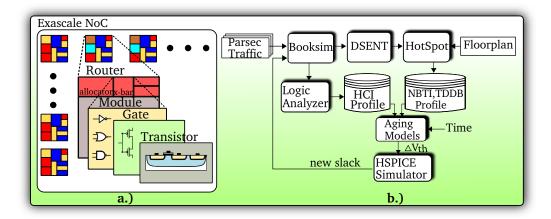

• Top-down Evaluation Platform: A top-down simulation platform was developed to provide a rigorous assessment of system reliability. The infrastructure spans the whole spectrum of design abstraction layers, from architectural simulation down to transistor-level analysis. In this process, several tools such as Booksim 2.0, DSENT 0.91, HotSpot 5.02, an in-house logic analysis tool and HSpice are integrated. These tools perform architectural simulation, power analysis, thermal analysis and delay degradation evaluation of major wearout mechanisms. Compared to the recently proposed state-of-the-art VICIS [9], the best routing algorithm improves QoS and long-term sustainability (Mean Time To Failure) of the system by 9% and 25%, respectively, while avoiding an increase in flit latency.

#### 1.3 HCI Tolerant NoC Router Microarchitecture

This work proposes a NoC router microarchitecture that lessens the aging effect of Hot Carrier Injections. HCI is an unrecoverable aging phenomena [10], which affects the components due to their dependence on switching activity [11]. Due to aggressive transistor scaling, the thinner gate dielectric in CMOS transistors increases the probability of HCI degradation. In fact, HCI can account for a major component of aging in a 10-year product lifetime [12]. To the best of the author's knowledge, none of the existing works consider HCI aging mitigation in the NoC architecture.

This research performs a holistic cross-layer analysis of HCI degradation in the NoC router microarchitecture. The crossbar structure of the router microarchitecture has been the focus of this study, due to its profound significance in dictating the router frequency [13]. Combining application-level traffic profile with bit-level logic analysis, it is found that the crossbar structure is highly vulnerable to HCI aging. Due to the data communication patterns in many-core applications, it is observed that a majority of gate-level switching activities are restricted to a small portion of the entire crossbar circuit topology, resulting in a large HCI degradation. To throttle HCI aging in the crossbar, this work proposes a series of low-overhead techniques that evenly distribute the switching activity in the crossbar, without affecting the architecture-level routing latency and bandwidth.

The contributions made through this work are:

- This work developed a cross-layer framework for HCI aging analysis of an NoC router.

The framework combines application traces, RTL gate-level simulation of a crossbar circuit, logic analysis, and HSPICE simulation of HCI degradation effect (Sections 4.2.2 and 4.4.3).

- An analysis of the switching activity of the crossbar, a major circuit in an NoC router using real-world applications and find that only a small group of gates account for most of the switching activity. On an average for PARSEC benchmarks, only 25% of the gates account for more than 75% of the switching activity, severely damaging some gates while leaving others unscathed (Section 4.2).

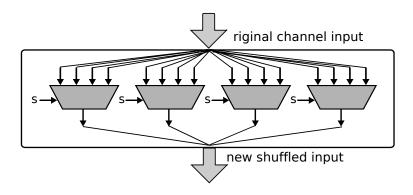

- A proposal for four schemes using low overhead techniques to evenly distribute the switching activity and minimize HCI degradation (Section 4.3). The four schemes are: Bit Cruising that distributes the high activity bits around the channel; Distributed Cycle Mode that exploits idle cycles in the NoC; Crossbar Lane Switching that manipulates the port in the crossbar by utilizing the virtual channels; and a combination of Bit-Cruising and Crossbar Lane Switching.

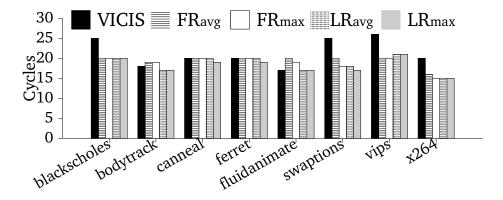

- A holistic evaluation of the proposals spanning full-system simulation down to RTL and gate-level HSPICE simulation (Section 4.5). The best schemes proposed in this work improve the switching activity distribution by up to 31% (ave: 19%). A maximum of 30% (ave: 26%) improvement in the clock cycle degradation, while the system performance degradation is reduced by up to 17.6% (ave: 11%) compared to the baseline scheme are also observed. The Energy Delay Product per Flit is improved by up to 27% (ave: 17%).

#### 1.4 Proactive Aging Management in Heterogeneous Network-on-Chips

This research studies reliability issues inherent in power-efficient Heterogeneous Network-On-Chip architectures. In particular, the asymmetric utilization seen in NoC components, substantially exacerbate aging degradation. For example, Mishra et al. observe that routers in the central region of the mesh can have more than 2X utilization compared to those near the peripheral region [14]. Such higher utilization in some NoC components can manifest as rapid aging-induced power-performance degradation in those components, causing system-wide deterioration.

To effectively tackle aging degradation in power-efficient NoCs, this work presents a novel adaptive routing algorithm that dynamically modifies traffic flow and exploits opportunities to avoid the use of buffered routers, while minimizing system-level power-performance impact. The proposed approach incorporates a Wearout Monitoring System (WMS) (composed of NBTI delay sensors) in NoC components, and combines architecture-level packet criticality during routing to relieve the heavy usage in aged components. Overall, the proposed routing algorithm can substantially reduce the effects of aging degradation in hNoCs, thereby assuring a graceful degradation in the communication architecture of emerging systems.

This work makes the following contributions:

- Reliability Analysis of an hNoC: This research presents an extensive study analyzing the impact of routing policies in an hNoC (Section 3.1). The analysis from this work shows an alarming increase in utilization asymmetry in certain hNoC components (by more than 1.35×), which can cause rapid aging degradation in those components, severely affecting system-level performance characteristics. In this context, a new opportunity in reliability-driven routing in an hNoC was uncovered, by demonstrating that a substantial portion of the data packets routed in the network are non-critical (i.e., system performance is insensitive to their latency). Thus, utilization in centrally placed buffered routers can be reduced by minimizing non-critical packets routed through them.

- Proactive Routing to Mitigate NoC Aging: This work developed a novel dynamic aging-aware routing algorithm based on architecture-level criticality information and accumulated wearout information using a proposed Wearout Monitoring

System (Section 3.2). To the best of the author's knowledge, this is the first work that uses the criticality information of packets to improve the reliability of NoCs.

• Holistic Evaluation: A holistic evaluation of the proposed algorithm is done by integrating: (a) SPICE-level simulation to estimate the combined effect of device aging based on circuit-level utilization and process variation (Section 3.3), (b) statistical timing analysis of synthesized hardware to accurately estimate the delay distribution under aging and expected usage pattern (Section 3.3), and (c) cycle accurate architectural simulation using GARNET and GEMS toolsets with multithreaded applications on a 16-core system with an hNoC (Section 3.4). Compared to the aging overhead seen in a state-of-the-art hNoC routing scheme [15], the best scheme developed in this work shows 38%, 53% and 29% improvement in network latency, system performance and EDPPF degradation (on average), respectively (Section 3.5).

#### 1.5 Fort-NoCs: Mitigating the Threat of a Compromised-NoC

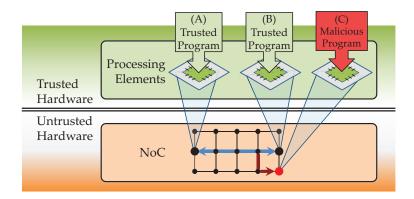

This research on security uncovers a novel and imminent threat to an emerging computing paradigm: MPSoCs built with third party IP NoCs. It is demonstrated that a compromised NoC (C-NoC) can enable a range of security attacks with an accomplice software component. To counteract these threats, a technique called Fort-NoCs<sup>1</sup> has been proposed, a series of schemes that work together to provide protection from a C-NoC in an MPSoC. Fort-NoCs's foolproof protection disables covert backdoor activation, and reduces the chance of a successful side-channel attack by "clouding" the information obtained by an attacker. Compared to recently proposed techniques, Fort-NoCs offers a substantially better protection with lower overheads.

This work shows that a malicious third party vendor can provide a compromised NoC by embedding a hardware trojan within the IP block. Such a trojan can facilitate a range of possible attacks with an accomplice software. For example, an accomplice software component can establish a covert communication with the NoC to snoop on the ongoing

<sup>&</sup>lt;sup>1</sup>Fort-NoCs is a word play between NoCs and Fort Knox–a security hardened structure housing US gold deposits.

data communication through the NoC, thereby stealing classified information. Many other types of attacks such as voluntary data corruption or denial of service are also possible.

The following contributions are made through this work:

- A new threat model stemming from a C-NoC design. This model can be a potent security threat as third party NoCs become more prominent in low-cost cloud computing on MPSoCs (Section 6.1).

- A detailed design of a C-NoC and evaluate its design footprint and runtime performance overhead. The rigorous analysis performed in this dissertation demonstrates that it is possible to realize this threat model with a minimal footprint, clearly showcasing the potency of the threat model that is uncovered in this work (Section 6.2).

- Fort-NoCs, a holistic layered approach to harden security on systems with a C-NoC: Node Obfuscation (NObf), Packet Certification (PC) and Data Scrambling (DS). The proposed techniques play complementary roles in hardware level protection by preventing the two-way communication between software and the hardware C-NoC, and introducing noise in the NoC data communication semantics with negligible overhead on performance and bandwidth of the NoC (Section 6.3).

- A thorough analysis of the proposed secure design solutions by measuring the associated power, area, and performance overheads. Compared to the recently proposed state-of-the-art NoC-MPU [16], the proposed Fort-NoCs offers compelling advantages in power-performance overheads and threat resilience from a C-NoC (Section 6.5).

# Chapter 2

# Literature Survey and Related Work

In this chapter, a comprehensive literature survey is done to build the foundation of this research. The relevant areas related to this study include the current state-of-theart work on power-performance, reliability and security optimizations in NoCs. To this end, this chapter is organized into the following sections: Section 2.1 explains recent work that tackle power-performance, reliability and security issues. The succeeding sections collate the information in Section 2.1 in order to clearly delineate the contribution of this dissertation. Section 2.2 positions this research in the realm of existing work on Exascale NoCs. Section 2.3 justifies the hNoC reliability research against existing works. In Section 2.4, the importance of addressing Hot-Carrier Injection is explained. Lastly, Section 2.5 discusses the current landscape of security research in NoCs.

#### 2.1 State-of-the-Art in NoC Research

This section explains the current state-of-the-art in reliability, power-performance and security research.

- BRAR [15]: BRAR stands for Buffered-Router Aware Routing. It is a routing technique that exploits the non-uniformity of router design in an hNoC. In a traditional hNoC, the flits can be misdirected when there is conflict in bufferless routers. BRAR decreases the probability that a flit is deflected by routing towards buffered routers. Overall, BRAR is optimized for a power-efficient hNoCs.

- Yin et al. [17]: Yin's work optimizes path routing in an hNoC that is used as a CPU-GPU communication platform. It is primarily motivated from the fact that GPU traffic can tolerate a slack. Since GPU traffic is usually bandwidth-sensitive, it

can tolerate a small delay without affecting its overall performance. Thus, packets can be routed using non-minimal paths to be able to optimize energy-efficiency.

- Li et al. [18]: Li's work optimizes the packets' latencies by identifying two types of traffic that are in the network. There are latency-critical packets and latency-noncritical packets. The former traffic is important as there prompt delivery dictates the performance of the whole program. Subsequently, latency-noncritical packets can be delayed without affecting the performance. Li created a run-time technique which leverages data-transaction and protocol information. By letting latency-critical traffic bypass pipeline stages, they are able to accelerate a program's performance.

- AGE-ADAP [19]: AGE-ADAP created an adaptive routing algorithm to relieve NBTI stress in heavily utilized routers and links. They introduced a new metric called Traffic Threshold per Epoch (TTpE) that limits the amount of traffic that a router can have in a time interval. By using a control system to adjust the TTpE, they are able to provide graceful aging degradation in NoCs.

- Fu et al. [20]: Fu's work optimizes the NoC architecture reliability for both process variation and NBTI effects. They improve the reliability profile of virtual channel allocation logic and registers. Fu's work require an online detector to detect the transistor degradation of both logic and register circuits. Using the detected values, the degradation can be controlled to ensure uniform aging.

- Vicis [9]: Vicis is an NoC design that can tolerate the loss of many network nodes due to aging. Each router node in Vicis has a built-in self test circuit that checks hard-faults in the system and corrects them by using ECC, port swapping and crossbar bypassing. Vicis can tolerate a large amount of errors (1 in 2000 gates) and can also operate while only half of its routers are fully functional.

- ROCO [21]: ROCO aims to design a low-latency, energy-efficient and reliable NoC.

ROCO decouples the arbitration and uses smaller crossbars for row and column decoding. By using many crossbars, ROCO is able to reduce the output port contention

probabilities compared to a baseline router. The modular design of ROCO allows graceful aging degradation in the even of hard-faults. Consequently, it also has less dynamic power.

- Park et al. [22]: Park et al. examined the impact of transient errors in the reliability of NoCs. They proposed novel techniques to tolerate or prevent from such errors. To handle soft link errors, they introduce a retransmission scheme that detects and retransmits flits that were corrupted temporarily. They claim that the design of their retransmission scheme has lower overhead compared to other works.

- BLESS [23]: BLESS is the first work that extensively evaluated the feasibility of using a complete bufferless network. They argue that buffers in modern NoCs consume enormous energy, occupy a large chip area and also increase the design complexity due to the circuits needed to manage them. Routing without buffers significantly reduce energy consumption while providing the same performance at lower network loads. BLESS can be used for processor/cache networks where network utilization is low.

- Abeyratne et al. [24]: Abeyratne et al. conducted several experiments on asymmetric high-radix topologies to explore network designs that can support thousands of processors. Asymmetric topologies optimize both local and global communication by matching the wire speed and the router speed. They used fast medium-radix router for local communication and a few slow high-radix routers for optimized global communication. They are able to achieve about 45% network latency improvement compared to a traditional mesh. case for on chip bufferless networks

- Kilo-NoC [25]: Kilo-NoC proposes an hNoC for scalability and QoS. They proposed a network that has few nodes providing QoS. Traffic requiring QoS are then routed towards this region before being sent to its final destination. They used elastic buffers to provide a fast communication path into and out of QoS region. By constraining QoS in a specific region with few routers, Kilo-NoC is able to provide QoS in an massive setting without severely compromising power consumption of the NoC.

- PVC [26]: PVC implements a Virtual Clock (VC) control flow with preemption capabilities in an on-chip network. They discuss the challenge of implementing a power and energy efficient VC flow in an on-chip network that has a smaller silicon budget compared to a traditional IP network. The preemption capability of the network allows PVC to prioritize critical traffic in order to maintain QoS in the system while requiring only a small amount of buffers compared to the traditional VC control flow. PVC employs a low-latency global acknowledgment network in order to facilitate preemption and retransmission of packets.

- Hosseini et al. [4]: Hosseini et al. present a new dynamic routing algorithm for NoCs serving SoCs. The routing algorithm they created has the ability to pinpoint both static and dynamic permanent failures. The algorithm is also able to distinguish between permanent failures and soft-errors by keeping track how many errors are encountered in a particular phase. The algorithm uses the acknowledgment system of a NoC to ensure that packets are correctly sent to the downstream router. In addition to reliability advantages, their algorithm can also distribute the load over the whole network by considering the stress factors in the system. The algorithm uses the queue length at each router as an indicator of network congestion.

- Explicit Path Routing [5]: Chaix et al. propose Explicit Path Routing (EPR), a deadlock-free adaptive routing algorithm. The goal of EPR is to limit latency degradation of packets in the NoC even under faulty conditions. Deadlock avoidance for EPR is implemented using a variant of the turn-restriction model. Essentially, some turns are prohibited depending on the path of the packet so as to break cycle dependencies. EPR also provides high performance under faulty conditions by studying the state of the network at runtime. Whenever the system is reconfiguring, an echo packet is sent, which finds the optimal path of a source-destination pair. Once the path of a faulty source-destination pair is determined, this path is used indefinitely.

- BFT-NoC [6]: Tsai et al. propose the Bidirectional Fault-Tolerant NoC technique that is capable of addressing both static and dynamic channel failures. By using bidirectional channels, a faulty router can be reached as long as one of its links is still functional. In contrast, schemes that use unidirectional links will result in unreachable nodes the moment one of its links becomes faulty. Under faultless conditions, BFT-NoC operates similarly as a traditional NoC router. However, once a fault is detected, BFT-NoC routers go through a reconfiguration phase where the channel mode (i.e. transmit or receive) is being determined based on network demand. This approach provides graceful degradation for NoCs.

- Zhang et al. [7]: Zhang et al. propose a reconfigurable routing algorithm that is deterministic, fault-tolerant, distributed and reconfigurable. The main idea of the algorithm is to create a path to route the packets through a cycle-free contour that surrounds a faulty router. Hence, restoring all broken paths caused by the faulty router. The algorithm uses 9 canonical contours of a mesh NoC to establish paths at runtime. Once a packet cannot find a route using the normal algorithm due to faults in the system, the routing path is changed by connecting the different contours to establish a path. Deadlock-avoidance is achieved by prohibiting specific turns in the path.

- FARM [27]: FARM stands for Fault-Aware Resource Management, a system-level fault-tolerant technique that uses dynamic application mapping to achieve optimal system performance while minimizing communication energy consumption. FARM's resource allocation algorithm also takes into account permanent, transient and intermittent faults in the system. The main idea of FARM is a feedback mechanism where system runtime metrics are gathered in order to determine the optimal task mapping. Based on current conditions, a multidimensional problem is solved at runtime to come up with a task mapping. FARM optimizes metrics such as manhattan distance of communicating tasks, link contention, and system fragmentation.

- Lan et al. [28]: Lan et al. present a study in Performance and Energy tradeoffs in reliable NoCs. The reliability issue considered in the work is that of ECC (Error Control Codes) hardware implemented in NoC routers. The work's main objective is to characterize the causes of energy consumed for fault tolerance hardware and also to provided a comparison among different ECC implementations. Note that the ECC only corrects errors present in the data plane. In contrast, errors can be also present in the control plane of the router (i.e. allocation, routing, arbitration etc ..). The ECC codes compared by the study are CRC4/8, DED, PAR, SEC, SECDED. It is found out that the retransmission of flits creates the biggest energy consumption as opposed to the different encoding and decoding HW required by ECC.

- For Forely Enhanced Runtime Verification to ensure NoC Functional Correctness, a scheme that complements the use of formal verification and runtime verification. It addresses the limitations of formal verification by creating a runtime technique that detects errors, and recovers from them. In Forever, a bare bones light-weight checker network is used to alert destination nodes of incoming packets in advance. Once a bug in the HW is detected (i.e. via an undelivered packet), the original packet is sent to the destination using the alternate checker network. This provides full functional coverage as long as the checker network is error-free. For EVER claims to recover errors within 30K cycles.

- NoCAlert [30]: Prodromou et al. proposes NoCAlert, an online and real-time fault detection scheme for NoCs. NoCAlert uses the concept of invariance checking. Similar to FoREVER, it uses micro-checker modules that essentially implements hardware assertions. The checker modules operate in lockstep unison with normal NoC operation, preventing the need for periodic or trigger-based self testing. NoCAlert claims 97% instantaneous detection of faults from the test vectors they have used. By using invariance checking, NoCAlert reduces the solution space of the errors that it needs to detect. This is because some of the errors in the system are harmless (i.e. a misrouted

flit can still reach its destination). As such, it provides good coverage at a very low overhead.

- StageNetSlice [31]: Gupta et al. propose StageNetSlice, a reconfigurable microarchitecture building block for resilient CMPs. StageNet relies on a reconfigurable network of replicated processor pipeline stages to maximize the lifetime of a chip. Hence, allowing graceful degradation of the microprocessor. Each pipe stage is replicated and are stitched together using a crossbar switch. StageNetSlice efficiently handles inter pipeline dependencies in order to come up with a fast distributed network design. As errors are manifested in the pipeline throughout its lifetime, the chip is also reconfigured in order to operate in an error-free manner.

- Siddiqua et al. [32]: Siddiqua et al. propose Recovery Boosting, a technique that addresses NBTI degradation in SRAM cells. NBTI affects SRAM cells when a logic "0" is stored in the cell. As such, Recovery Boosting counteracts this effect by engaging PMOS devices in recovery mode (i.e. biasing to Vdd) during times of inactivity in the system. Recovery Boosting is implemented in the physical register file of a processor to enhance its reliability. To integrate Recovery Boosting in a modern processor, the control circuitry of the Register File must be modified to support Recovery mode when a register is not used. Recovery Boosting has been shown to provide over 50% static noise margin improvement for the register file.

- Fiorin et al. [33]: Fiorin et al. propose a scheme to enforce security of memory accesses in NoCs. The proposed idea uses data protection units (DPU), implemented in the network interfaces, to authenticate memory accesses in the system. All the DPUs are managed by a central unit called the Network Security Manager. The DPUs, configured by the NSM, serves as a firewall that checks and limit the access rights of nodes accessing data and instructions in shared memory. It divides the resources in the system (i.e. memory, IP) into secure/unsecure areas and limits accesses based on

user policies. As long as the NSM is uncompromised, the system can be considered secure.

- Diguet et al. [34]: Diguet et al. proposed a NoC architecture that protects SoC against attacks such as: Hijacking, secret information extraction and Denial of Service. This work uses a 4-step approach towards SoC security. First, a single centralized, dedicated and secured master IP must supply all security-related configurations of the chip. Second, the network interfaces must be enhanced in order to enforce access rights restriction. Third, there must be a two separate VCs in the network in order to separate communication and security data. Fourth, holistic integration of previous steps to determine if the SoC security has been compromised.

- Gebotys et al. [35]: Gebotys et al. proposed a framework for security on NoC enabled technologies. Security is addressed in both the transport layer (i.e. network) and the application layer (i.e. core). For the transport layer security, each IP core has a security wrapper and a module that securely hides private keys are included in each NoC router. This model prevents unencrypted private keys from ever leaving the cores and NoC. At the core level, an obfuscation method is used to hide the correlation between a hash calculation and its power profile. This two-pronged approach creates a secure system that is immune to probing and side-channel attacks.

- Kapoor et al. [36]: Kapoor et al. proposed a framework that uses Authenticated Encryption and Session Keys to implement security in a NoC. Encryption and decryption of keys are implemented in the network interfaces of every IP core. Communications between secure IP cores use a predefined key while communications between secure and non-secure cores uses a dynamically generated session key. By continuously changing the key, the NoC can determine if the system has been attacked. DoS attacks are prevented using counters inside the NoC routers while unauthorized memory accesses are prevented using an access rights table.

- SurfNoC [37]: Wassel et al. proposed SurfNoC: a low latency and provably non-interfering approach to secure NoCs. The aim of SurfNoC is to provide security by maximizing temporal and spatial separation of different flows in the system. SurfNoC implements static isolation of flows in the network without sacrificing NoC performance. Static isolation of resources are desired to prevent sharing of information through side-channels. The key to SurfNoC's approach is to do network scheduling in wave manner. This allows multiple flows in the network to co-exist in a non-interfering nature while also avoiding the overheads of a cycle-by-cycle time multiplexing.

- Wang and Suh [38]: Wang and Suh proposed an efficient architecture for preventing timing-channel attacks in a network on chip. Their schemes uses a priority based arbitration and a static limit mechanism to provide one-way information-leak protection. To do this, the authors came up with a Reversed Priority with Static Limit algorithm. This algorithm assigns a higher priority to low-security traffic so that its behavior is not affected by high-security traffic. Hence, preventing a one-way information leak. The static limit is imposed for low-security applications in order to prevent it from doing a Denial-of-Service attack on the high-security application.

- Illinois Malicious Processor [39]: King et al. proposes many of techniques on how to design a malicious hardware such as a processor. Their main claim is that instead of creating a hardware that can support one type of attack, a flexible hardware can be created to allow powerful and general purpose attacks. The HW overhead for creating such "attack-infrastructure" are relatively small. The authors demonstrate the potency of a HW attack through a login backdoor. A circuitry inside a modern processor that can be used to easily provide an attacker complete privileged access into the system.

#### 2.2 Reliability Considerations for Exascale Systems

Emerging systems, with hundreds of billions of transistors, are likely to have many faults, even at the point of tape-out [40]. These faults can impact both processing cores as

well as NoC components, drastically reducing their functionality. Many recent NoC works target these faulty components, and outline a plethora of techniques to tolerate faults and sustain successful communication between two nodes [4–7, 27–30].

In the realm of exascale computing, most research on exascale NoCs have revolved around performance, energy efficiency, QoS and scalability. Moscibroda et al. explore the use of bufferless routers for a scalable and energy-efficient NoC network [23]. Abeyratne et al. explore scalable, asymmetrical high-radix NoC topologies for use in a Kilo-Core systems [24]. Grot et al. studied scalable QoS incorporation in exascale systems [26]. However, system resiliency is also fast becoming a first-class design constraint as designers continue to progress with Moore's law. Bhardwaj et al. explore aging aware routing in NoCs, but do not consider exascale systems and QoS implications [19,41]. Similarly, several recent works explore el fault-tolerant routing in small-medium scale NoCs, but do not consider exascale NoCs. One of the most prominent works is VICIS by Fick et al. that provides a complete infrastructure for network recovery in the face of component failures [9]. Since most of the works in exascale focused on solving individual problems, they failed to realize that the reliability of the system is severely compromised when several of these proposed ideas are combined. To the best of the author's knowledge, this is the first work to clearly identify the reliability tension in exascale NoCs, caused by scaling and supporting QoS. The proposed novel approach aims to boost NoC sustainability without sacrificing QoS and scalability.

#### 2.3 Reliability Design in hNoCs

Few works beyond the BRAR [15] investigate routing approaches in an hNoC. Yin et al. [17] proposed an energy efficient non-minimal path routing algorithm for a heterogeneous NoC running a CPU-GPU system by exploiting the slack provided by the bandwidth-sensitive GPU traffic. In essence, they classify criticality of flits as the source of the traffic (GPU/CPU). Li et al. present runtime techniques to reduce the overall network latency of latency-critical packets by letting them bypass the router pipeline stages, hence improving performance [18].

While previous works focus on using criticality to improve performance and power efficiency in a router-homogeneous NoC, the technique proposed in this work is the first to consider criticality in the context of reliability-driven routing in heterogeneous NoCs. The routing technique mitigates the effect of aging degradation by relieving the burden on routers that are likely to be highly degraded, while minimizing the system level impact of non-optimal flow control. Moreover, the WMS and deflection based schemes can also be used in homogeneous NoCs to add aging-aware functionality.

## 2.4 HCI-Aware Design of NoCs

The aggressive scaling in CMOS technology has made reliability a primary design constraint in modern computing systems. While there has been a wide scope of studies tackling different reliability issues (NBTI, TDDB, HCI) in processing elements [31, 42], there is only a limited number of works which address wear-out mitigation in the on-chip communication infrastructure of such systems. Bhardwaj et al. implemented a dynamic routing algorithm to equalize NBTI and electromigration aging across the on-chip network [19]. Fu et al. created new virtual channel allocation and routing algorithms in order to improve process variation and NBTI effects in key components of the router [20]. Park et al., Fick et al., and Kim et al. explored fault tolerant NoC architectures by decoupling modules and having redundancies in order to recover from intermittent errors in the network or provide graceful degradation [9, 21, 22].

Most of the studies mentioned above focus on recovering from intermittent errors or minimizing NBTI effect on storage elements by balancing the duty cycle. On the contrary, the technique proposed here will focus on HCI, an unrecoverable aging phenomena that affects combinational components. HCI mitigation presents a different set of challenges because of its dependence on the switching activity of transistors, as opposed to NBTI which depends only on the input bias. To the best of the author's knowledge, the proposed scheme in this work will be the first work to tackle HCI in an NoC router microarchitecture.

# 2.5 Landscape of Security for NoCs

A vast amount of recent works focus on hardware and software security, primarily to address a problem of growing importance. The discussion in this section is focused on NoC security, which is most relevant to the contribution of this research.

The current state-of-the-art in NoC security revolves around protecting information traveling in the network against side channel, physical and software attacks. Table 2.1 presents a high-level comparison of existing works on NoC security based on four major factors. Similar to software protection mechanisms, many existing works provide access control by monitoring the memory addresses (e.g., *Data Protection Unit (DPU)* proposed by Fiorin et al. [33], firewall from Sonics [43], access control on memory banks by Diguet et al. [34]). Some proposals aim to use encrypted data transmission over the NoC (e.g., [35,36]) or partition the NoC into separate zones based on trust [37,38]. In the industry, ARM has approached trusted computing through its TrustZone platform [44]. The idea is to establish secure and non-secure states throughout the chip. By changing the security mode of a component along with safety checks, information leaking from secure to non-secure areas are prevented.

The work presented in this dissertation explores a new threat model orthogonal to these works. First, it is assumed that the hardware trojan is embedded in the NoC itself, whereas others assume a trustworthy NoC. Second, it is demonstrated that information can be extracted from the NoC without relying on memory access (either through on-chip cache or off-chip memory). Third, it is also assumed that an accomplice software thread exists, which acts as the orchestrator of the attack. The hardware-software coalition in the proposed threat model is similar to the Illinois Malicious Processor (IMP) [39]. However, the IMP does not consider the threat of a C-NoC.

Table 2.1: Comparison of threats in NoCs.

|              | Trojan $\operatorname{Loc}^a$ | $\mathbf{IS}^b$ | $\mathbf{Prot}^c$ | $\mathbf{T}\mathbf{M}^d$ |

|--------------|-------------------------------|-----------------|-------------------|--------------------------|

| Fort-NoCs    | NoC                           | NoC             | NI                | S/W                      |

| DPU [33]     | S/W                           | Mem             | NI                | _                        |

| KeyCore [35] | S/W                           | Mem             | NI                | _                        |

| surfNoC [37] | S/W                           | S/W             | NoC               | _                        |

| AE [36]      | S/W                           | Mem             | NI                | _                        |

| IMP [39]     | $\mu$ P                       | $\mu P/Mem$     | _                 | S/W                      |

| NoC-MPU [16] | S/W                           | Mem             | NI                | _                        |

<sup>&</sup>lt;sup>a</sup> The part of the system where a trojan is inserted.

<sup>b</sup> The part of the system where the information is stolen.

<sup>c</sup> The part of the system where a protection mechanism is implemented to prevent an attack.

<sup>d</sup> The triggering mechanism in case of a hardware trojan.

# Chapter 3

# Reliability for Heterogeneous NoCs

This chapter discusses the technique developed in this work that addresses aginginduced degradation in hNoCs. The approach created is based on the combination of packet-criticality information and dynamic routing algorithms.

# 3.1 Motivation

In this section, the proposed scheme for mitigating aging effects in an hNoC is discussed by demonstrating two important circuit-architectural characteristics. First, it is shown that existing routing policies in a typical hNoC can lead to an alarming rise in the utilization asymmetry, exacerbating the NoC reliability challenge (Chapter 3.1.1). Second, the criticality of network packets in an NoC running multithreaded applications are analyzed to identify opportunities of improving reliability by exploiting packet non-criticality (Chapter 3.1.2).

Recently-proposed heterogeneous NoC designs exploit the non-uniform traffic across routers to proportion routing resources [14]. Zhao et al. [15] further improve performance by employing a routing algorithm that leverages the non-uniform structure of the network to move data along buffered routers to keep packets on their optimal paths. Routing through the buffered routers prevents these packets from being deflected arbitrarily by bufferless routers, which can increase their network latency. However, this routing approach overburdens the buffered routers as a majority of the flits (flits are the units of information flow in NoC networks) use buffered routers as a part of their pathways.

# 3.1.1 Utilization Asymmetry in Heterogeneous NoCs

The setup used in this study is shown in Figure 3.1(a). The Buffered Router Aware Routing (BRAR) routing algorithm from Zhao et al. [15] is used. Buffered routers are placed identically as shown in their work. BRAR routes flits along buffered routers to decrease the chance of packets deflected farther from their destination (Figure 3.1(b)). However, if there is output port contention, the flit is stored in the buffer and delayed for another cycle. In contrast, the routing on bufferless routers (Figure 3.1(c)) needs to deflect flits towards a different direction because once a packet loses arbitration for the switch, it will be sent out to any free port. Two out of three times, the packet will be sent out towards a non-optimal direction.

Figure 3.2 shows the increase in utilization asymmetry of the buffered routers when using the BRAR algorithm (distribution of buffered and bufferless routers are shown in Figure 3.1(a)). All 16 routers in a  $4 \times 4$  NoC mesh are shown, where the numbers in each router indicate the percentage increase in utilization compared to a homogeneous NoC employing XY routing. Results shown are average across several multithreaded PARSEC benchmarks used in this study. It has been observed that the centrally placed routers in the hNoC show 23–82% increase in utilization, while all of the peripheral routers show a range of reduced utilization. Compared to the homogeneous NoC, this hNoC employing BRAR routing shows  $1.35 \times$  increase in utilization asymmetry which ultimately leads to a more than  $2 \times$  increase in timing degradation on the buffered routers.

## 3.1.2 Criticality of Different Flits in NoCs