Utah State University DigitalCommons@USU

All Graduate Theses and Dissertations

**Graduate Studies**

5-2016

# Exploiting Adaptive Techniques to Improve Processor Energy Efficiency

Hu Chen Utah State University

Follow this and additional works at: https://digitalcommons.usu.edu/etd

Part of the Electrical and Computer Engineering Commons

### **Recommended Citation**

Chen, Hu, "Exploiting Adaptive Techniques to Improve Processor Energy Efficiency" (2016). *All Graduate Theses and Dissertations*. 4985. https://digitalcommons.usu.edu/etd/4985

This Dissertation is brought to you for free and open access by the Graduate Studies at DigitalCommons@USU. It has been accepted for inclusion in All Graduate Theses and Dissertations by an authorized administrator of DigitalCommons@USU. For more information, please contact digitalcommons@usu.edu.

## EXPLOITING ADAPTIVE TECHNIQUES TO IMPROVE PROCESSOR ENERGY EFFICIENCY

by

Hu Chen

A dissertation submitted in partial fulfillment of the requirements for the degree

of

## DOCTOR OF PHILOSOPHY

in

**Electrical Engineering**

Approved:

Sanghamitra Roy, PhD Major Professor Koushik Chakraborty, PhD Committee Member

Ryan Gerdes, PhD Committee Member Rose Hu, PhD Committee Member

Haitao Wang, PhD Committee Member Mark R. McLellan, PhD Vice President for Research and Dean of the School of Graduate Studies

UTAH STATE UNIVERSITY Logan, Utah

2016

Copyright © Hu Chen 2016

All Rights Reserved

#### ABSTRACT

#### Exploiting Adaptive Techniques to Improve Processor Energy Efficiency

by

Hu Chen, Doctor of Philosophy Utah State University, 2016

Major Professor: Sanghamitra Roy, PhD Department: Electrical and Computer Engineering

Rapid device-miniaturization keeps on inducing challenges in building energy efficient microprocessors. As the size of the transistors continuously decreasing, more uncertainties emerge in their operations. On the other hand, integrating more and more transistors on a single chip accentuates the need to lower its supply-voltage. This dissertation investigates one of the primary device uncertainties — timing error, in microprocessor pipeline; as well as, the energy trade-off between processor components in Near-Threshold Computing (NTC) era. Using rigorous cross-layer methodology, this dissertation identifies novel opportunities lying in microprocessor workload, and the shifted processor performance bottleneck in NTC era. Then it proposes various innovative techniques to exploit these opportunities to maintain processor energy efficiency, in the context of emerging challenges. Evaluated with the cross-layer methodology, the proposed approaches achieve substantial improvements in processor energy efficiency, compared to other start-of-art techniques.

(91 pages)

## PUBLIC ABSTRACT

Exploiting Adaptive Techniques to Improve Processor Energy Efficiency

by

Hu Chen, Doctor of Philosophy Utah State University, 2016

Major Professor: Sanghamitra Roy, PhD Department: Electrical and Computer Engineering

As technology advances, the size of transistor — the basic building block of microprocessors, continues shrinking. The downscaled transistor will make its manufacture process become less controllable, and its operation less predictable. Moreover, smaller transistor size will lead to higher volume of transistors on a single chip, thus increases the chip power consumption. This dissertation proposes various techniques to efficiently tolerate the uncertainties in microprocessors. Also, it proposes an innovative design paradigm to build energy-efficient processor under ultra-low supply-voltage. Evaluated with rigorous methodology, the proposed approaches achieve significant improvement in processor energy efficiency, compared to other state-of-art techniques. To my wife, Jing and our adorable son Jacob

#### ACKNOWLEDGMENTS

Firstly, I would like to express my sincere gratitude to my advisor Dr. Sanghamitra Roy, and my co-advisor Dr. Koushik Chakraborty for the continuous support of my Ph.D study and related research, for their patience, motivation, and immense knowledge. Their guidance helped me in all the time of research and writing of this thesis. Without it, my whole Ph.D study and research would not be never become possible.

I would like to thank all of my supervisory committee: Dr. Rose Hu, Dr. Ryan Gerdes, Dr. Haitao Wang, and Dr. Ming Li, for their insightful comments and encouragement that have incented me to widen my research from various perspectives.

My sincere thanks also goes to my fellow labmates in USU Bridge Lab, for the stimulating discussions, for the sleepless nights we were working together before deadlines, and for all the fun we have had in the last four years. I would like to thank Yiding, Jason and Dean for their guidance as I started my research; thank Manzi, Shamik, Prabal and Atif for withstanding the deadline pressure with me; thank to Shayan, Rajesh and Harshita for all the fun we had in the 2014 DAC trip; thank to Saptarshi for the fun conversations we had about life; thank to all the students who have helped me in one way or another: Brennan, Mohammed, McCabe, Brian, Andrew, Kenneth, Michael, Kenyon, Kurt and Chidham.

I would like to thank the ECE Department and all of the staff members, for giving me the opportunity to pursue my PhD degree. I am very thankful to Mary Lee Anderson, Kathy Phippen and Tricia Brandenburg for the invaluable support in supporting my Ph.D study in many ways.

Last but not the least, I would like to thank my family: my wife Jing and my son Jacob, for being my everlasting source of joy and motivation; my father for his impact on my life; my mother for her unconditional love.

## CONTENTS

| AI            | BSTI                     | ii ii                                                                                                                                                                                                                                                                                                                                                                                  | ii                                                                       |

|---------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| ΡŪ            | JBLI                     | C ABSTRACT ir                                                                                                                                                                                                                                                                                                                                                                          | v                                                                        |

| A             | CKN                      | OWLEDGMENTS v                                                                                                                                                                                                                                                                                                                                                                          | /i                                                                       |

| $\mathbf{LI}$ | ST C                     | OF TABLES                                                                                                                                                                                                                                                                                                                                                                              | x                                                                        |

| $\mathbf{LI}$ | ST C                     | DF FIGURES x                                                                                                                                                                                                                                                                                                                                                                           | ci                                                                       |

| 1             | <b>INT</b><br>1.1        | Contribution of This Dissertation       1.1.1         Conference Papers       1.1.1                                                                                                                                                                                                                                                                                                    | 1<br>2<br>2<br>3                                                         |

| 2             | LIT<br>2.1<br>2.2<br>2.3 | State-of-the-Art Works in Processor Reliability and Energy-Efficiency2.1.1Analysis and Modeling of Device Reliability2.1.2Efficiently Coping with Device Timing Uncertainties at Circuit Level2.1.3Architectural Strategies to Efficiently Tolerate Device Timing Variations2.1.4Fundamental Principles in NTC Era2.1.5NTC Design Techniques1Tackling Timing-Error in Microprocessors1 | $\begin{array}{c} 4 \\ 4 \\ 4 \\ 6 \\ 8 \\ 1 \\ 2 \\ 5 \\ 7 \end{array}$ |

|               |                          | RP: DYNAMICALLY ADAPTABLE RESILIENT PIPELINE DE-                                                                                                                                                                                                                                                                                                                                       |                                                                          |

| SI            |                          | IN MICROPROCESSORS 1                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |

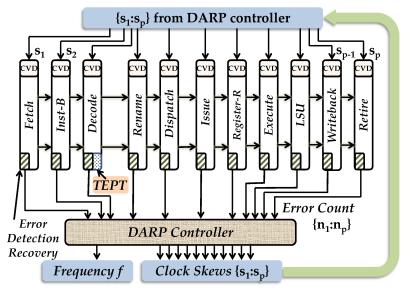

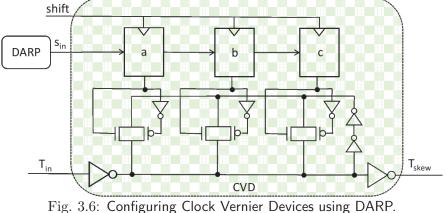

|               | $3.1 \\ 3.2$             |                                                                                                                                                                                                                                                                                                                                                                                        | $\frac{9}{1}$                                                            |

|               | 0.2                      | 3.2.1 Sensitized Pipe Stage Delay                                                                                                                                                                                                                                                                                                                                                      | 1                                                                        |

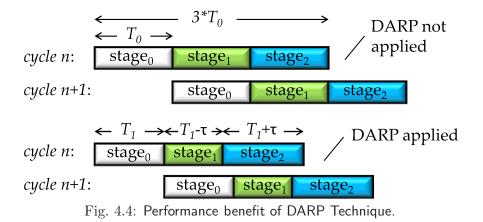

|               | 3.3                      | Dynamically Adaptable Resilient Pipeline23.3.1DARP overview23.3.2Exploiting Early Error Prediction2                                                                                                                                                                                                                                                                                    | 15<br>16<br>16<br>16<br>18                                               |

|               | 3.4                      | Methodology                                                                                                                                                                                                                                                                                                                                                                            | 1<br>1<br>2<br>3                                                         |

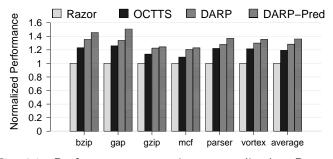

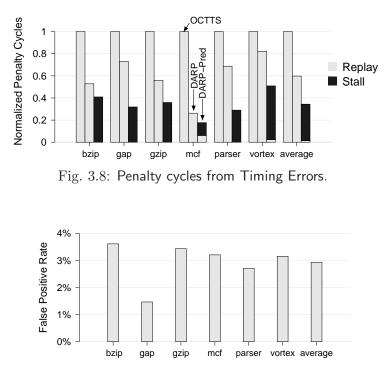

|               | 3.5                      | Experimental Results33.5.1Comparative Schemes3.5.13                                                                                                                                                                                                                                                                                                                                    | 3<br>3<br>4                                                              |

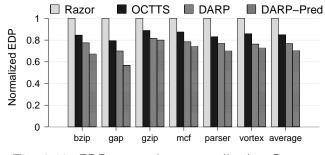

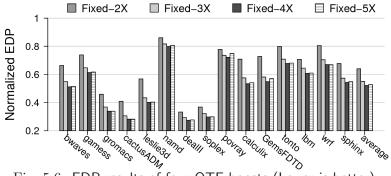

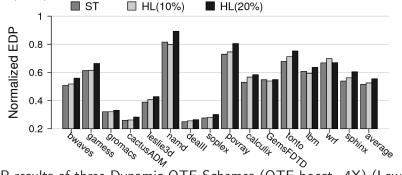

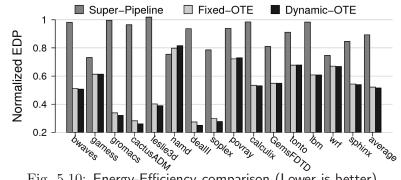

|      | $3.5.3 \\ 3.5.4$                            | Energy-Efficiency and Power-Efficiency Comparison35Power Overhead of DARP36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 0.0.1                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                             | P: DYNAMICALLY ADAPTABLE RESILIENT PIPELINE DE-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |                                             | ULTICORE PROCESSORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1  | -                                           | round and Contributions of This Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

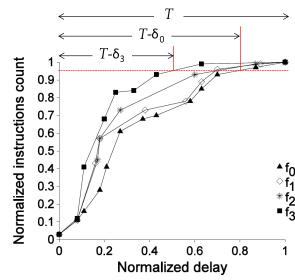

| 4.2  | Motiv                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

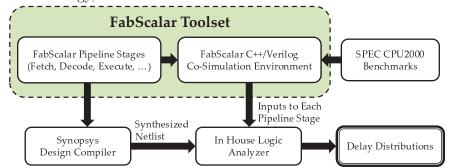

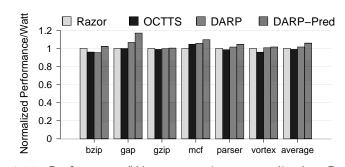

|      | 4.2.1                                       | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

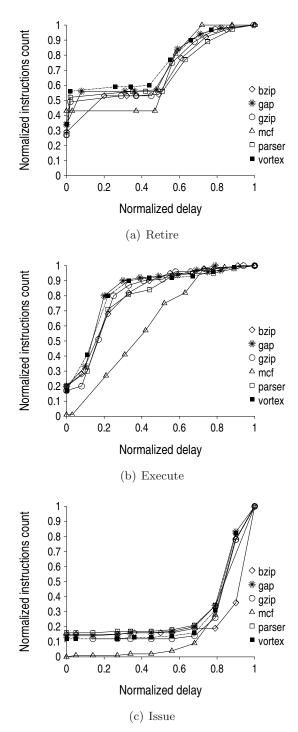

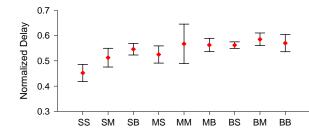

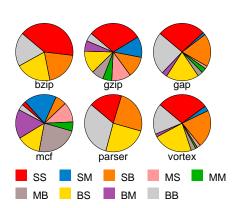

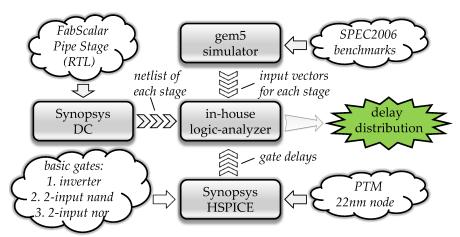

|      | 4.2.2                                       | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.9  | 4.2.3                                       | Significance $\dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

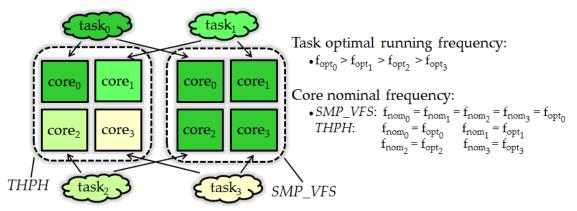

| 4.3  |                                             | P in Multicore Processor       42         TUDU A life to the second s |

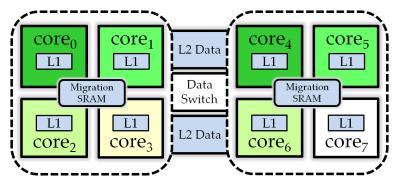

|      | 4.3.1                                       | THPH Architecture   43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | 4.3.2                                       | DARP Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | 4.3.3                                       | Potential of DARP in THPH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      | 4.3.4                                       | Integrating DARP with THPH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4.4  |                                             | $dology \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|      | 4.4.1                                       | Architecture Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|      | 4.4.2                                       | Circuit Layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      | 4.4.3                                       | Timing Error Simulation Methodology    49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4.5  |                                             | imental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | 4.5.1                                       | Comparative Schemes For DARP-MP 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

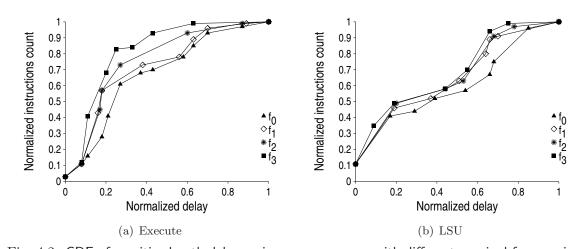

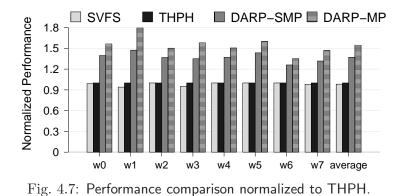

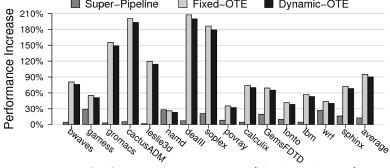

|      | 4.5.2                                       | Performance Comparison 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

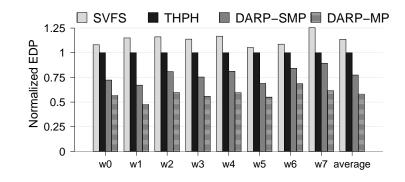

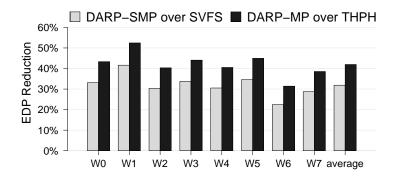

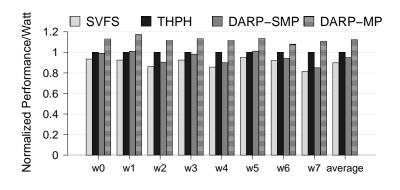

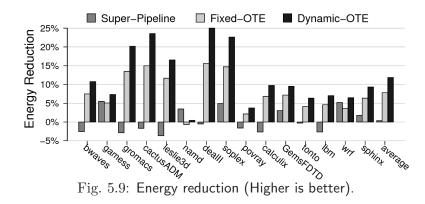

|      | 4.5.3                                       | Energy-Efficiency and Power-Efficiency Comparison 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|      | 4.5.4                                       | Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5 OP | PORT                                        | UNISTIC TURBO EXECUTION IN NTC: EXPLOITING THE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                             | I SHIFT IN PERFORMANCE BOTTLENECKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.1  |                                             | round and Contributions of This Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

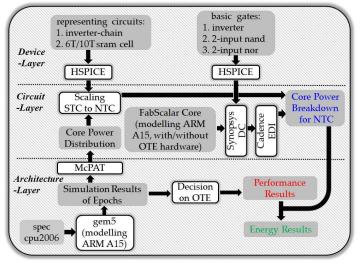

| 5.2  | Motiv                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 0.2  | 5.2.1                                       | Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

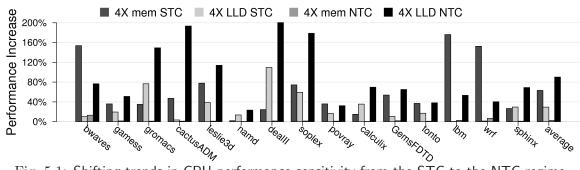

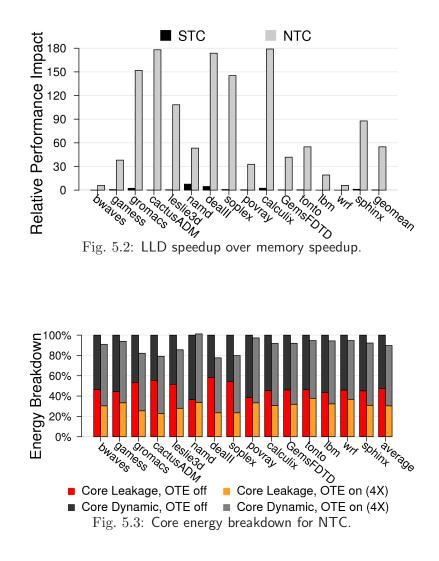

|      | 5.2.2                                       | Performance Bottlenecks in NTC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

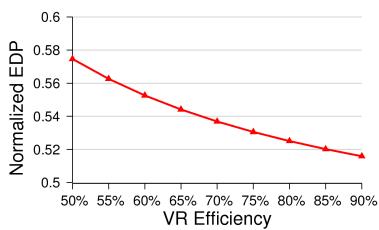

|      | 5.2.3                                       | Energy Efficiency Perspective of OTE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

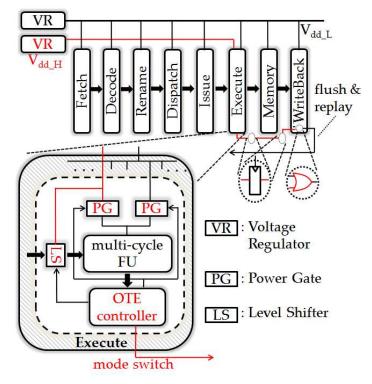

| 5.3  |                                             | rtunistic Turbo Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.0  | 5.3.1                                       | OTE Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |